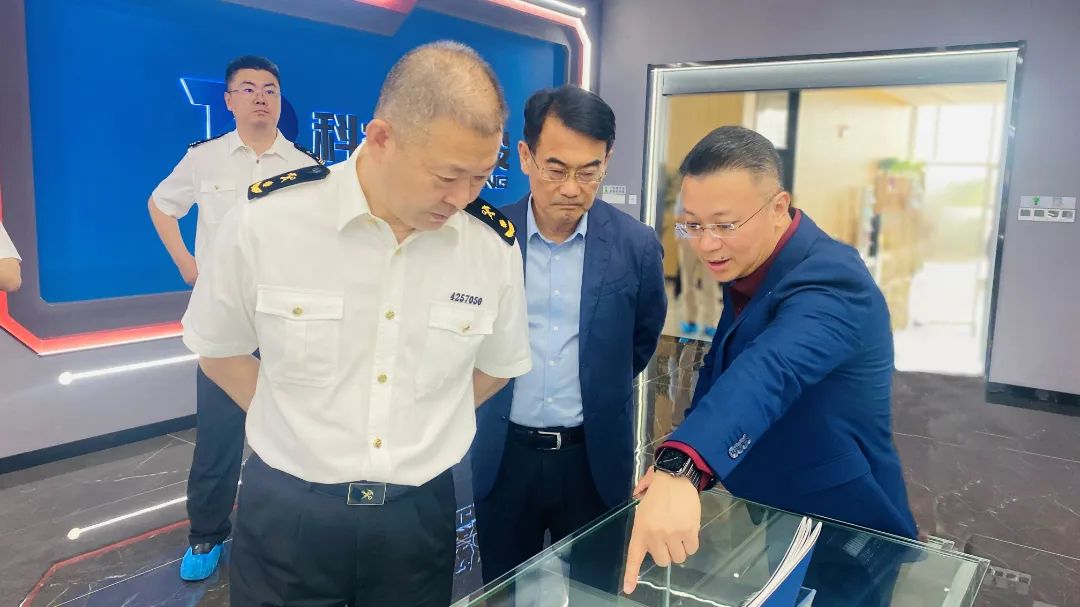

山东副省长周立伟调研日照市工业高质量发展等工作

6月26日,山东副省长周立伟调研日照市工业高质量发展等工作。他强调,要深入学习贯彻习近平总书记关于工业经济发展的重要论述和对山东工作的重要指示要求,把推动高质量发展作为首要任务,将工业经济摆在突出位置、作为“头号工程”来抓,为稳定经济运行提供坚实支撑。省政府副秘书长王健,市委副书记、市长李在武,市委常委、副市长贾刚参加。

在日照港,周立伟听取港口发展工作汇报,仔细询问铁矿石装卸运输、自动化集装箱码头建设、绿色环保作业、安全防范等情况,要求加快建设大宗干散货智慧绿色示范港口,实现环保、安全和效率多赢。来到中央活力区规划展示中心,周立伟对日照精致城市建设和阳光海岸绿道等民生实事给予肯定,叮嘱相关部门抓好高层建筑消防安全。在亚太森博浆纸、科睿特控股、山钢日照公司、日钢集团,周立伟走进生产车间,现场检查有关企业主控室安全隐患、应急预案台账,与企业负责人深入交流,详细了解产能和能耗煤耗、生产设备、环保投入、安全监测报警操作等情况,希望企业守牢安全底线,开足马力抓生产,加大技术攻关和产品创新投入,加强产业上下游衔接,提升生产效益和核心竞争力。

调研中,周立伟充分肯定了日照市稳定工业经济运行、实施工业倍增行动等工作。他强调,工业是国民经济的“压舱石”,工业稳则经济稳。日照临港产业基础好、特色鲜明,要认真落实省委、省政府决策部署,扎实推进制造业绿色低碳转型,加力提速工业经济高质量发展。要抓住当前重要窗口期,狠抓工业运行调度,聚焦钢铁、浆纸等支柱产业,对骨干企业和重要增长点靠前服务,抓好惠企政策落实和指导服务,巩固稳中向好态势。要大力推进科技创新,培育壮大新一代信息技术等战略性新兴产业,不断增创新动能、新优势。要时刻绷紧安全弦,压紧属地管理、部门监管、企业主体各方责任,抓实重点领域和重大事故隐患专项排查整治,以针对性措施严防各类事故发生。